# Intro to Computer Arch

**CARP Research Presentation 1**

# First: Languages

### What about Hardware?

#### Hardware Description Languages (HDL)

#### Common HDLs

- VHDL

- Verilog / SystemVerilog

Used to describe hardware - like a CPU

Compiles to a "netlist" rather than assembly

Used in testing or for deployment on FPGAs

### What does a computer (CPU) do?

#### CPU

**Executes instructions**

Needs a common language to work on

- Compilers

- Assembly

Different modules, execution blocks, for different purposes

Forms of speeding up instruction execution (see next presentation 66)

# How do the instructions execute?

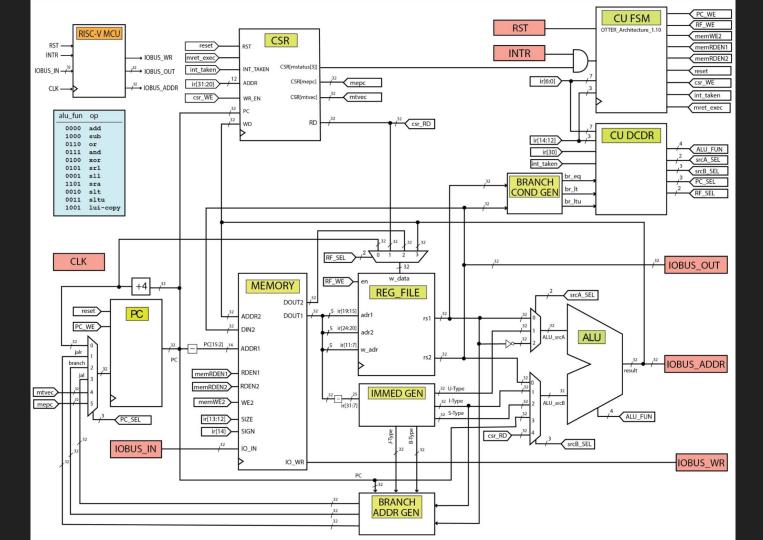

#### RISC-V OTTER Assembly Instruction Overview

Table 12 lists RISC-V OTTER instructions; shaded instructions are pseudoinstructions

| Instru | ıction      | Description                              | RTL                                                        | Comment            |

|--------|-------------|------------------------------------------|------------------------------------------------------------|--------------------|

| add    | rd,rs1,rs2  | addition                                 | X[rd] ← X[rs1] + X[rs2]                                    |                    |

| addi   | rd,rs1,imm  | addition with immediate                  | X[rd] ← X[rs1] + sext(imm)                                 |                    |

| and    | rd,rs1,rs2  | bitwise AND                              | $X[rd] \leftarrow X[rs1] \cdot X[rs1]$                     |                    |

| andi   | rd,rs1,imm  | Bitwise AND immediate                    | X[rd] ← X[rs1] · sext(imm)                                 |                    |

| auipc  | rd,imm      | add upper immediate to PC                | $X[rd] \leftarrow PC + (sext(imm) << 12)$                  |                    |

| beq    | rs1,rs2,imm | branch if equal                          | PC ← PC + sext(imm) if (X[rs1] == X[rs2])                  | imm ≠ value        |

| beqz   | rs1,imm     | branch if equal to zero                  | PC ← PC + sext(imm) if (X[rs1] == 0)                       | imm ≠ value        |

| bge    | rs1,rs2,imm | branch if greater than or equal          | PC ← PC + sext(imm) if (X[rs1] ≥ <sub>s</sub> X[rs2])      | imm ≠ value        |

| bgeu   | rs1,rs2,imm | branch if greater than or equal unsigned | PC ← PC + sext(imm) if (X[rs1] ≥ <sub>u</sub> X[rs2])      | imm ≠ value        |

| bgez   | rs1,imm     | branch if greater than or equal to zero  | $PC \leftarrow PC + sext(imm) \text{ if } (X[rs1] \ge 0)$  | imm ≠ value        |

| bgt    | rs1,rs2,imm | branch if greater than                   | PC ← PC + sext(imm) if (X[rs1] > <sub>s</sub> X[rs2])      | imm ≠ value        |

| bgtu   | rs1,rs2,imm | branch if greater than unsigned          | PC ← PC + sext(imm) if (X[rs1] > <sub>u</sub> X[rs2])      | imm ≠ value        |

| bgtz   | rs1,rs2,imm | branch if greater than zero              | PC ← PC + sext(imm) if (X[rs1] > <sub>s</sub> 0)           | imm ≠ value        |

| ble    | rs1,rs2,imm | branch if less than or equal             | PC ← PC + sext(imm) if (X[rs1] ≤ <sub>s</sub> X[rs2])      | imm ≠ value        |

| bleu   | rs1,rs2,imm | branch if less than or equal (unsigned)  | PC ← PC + sext(imm) if (X[rs1] ≤ <sub>u</sub> X[rs2])      | imm ≠ value        |

| blez   | rs1,rs2,imm | branch if less than or equal zero        | PC ← PC + sext(imm) if (X[rs1] ≤ <sub>s</sub> 0)           | imm ≠ value        |

| blt    | rs1,rs2,imm | branch if less than                      | PC ← PC + sext(imm) if (X[rs1] < <sub>s</sub> X[rs2])      | imm ≠ value        |

| bltz   | rs1,imm     | branch if less than zero                 | PC ← PC + sext(imm) if (X[rs1] < <sub>s</sub> 0)           | imm ≠ value        |

| bltu   | rs1,rs2,imm | branch if less than (unsigned)           | PC ← PC + sext(imm) if (X[rs1] < <sub>u</sub> X[rs2])      | imm ≠ value        |

| bne    | rs1,rs2,imm | branch if not equal                      | PC ← PC + sext(imm) if (X[rs1] ≠ X[rs2])                   | imm ≠ value        |

| bnez   | rs1,imm     | branch if not equal to zero              | $PC \leftarrow PC + sext(imm) \text{ if } (X[rs1] \neq 0)$ | imm ≠ value        |

| call   | label       | branch to subroutine                     | X[rd] ← PC + 8; PC ← &symbol                               | imm ≠ value        |

|        |             | WARNING: overwrites X6                   | (rd=X1 if rd omitted)                                      | overwrites X6      |

| csrrc  | rd,csr,rs1  | control & status reg read and bit clear  | X[rd] ← CSR[csr]; CSR[csr] ← CSR[csr] & ~rs1               | clears part of reg |

| csrrs  | rd,csr,rs1  | control & status reg read and bit set    | X[rd] ← CSR[csr]; CSR[csr] ← CSR[csr]   rs1                | sets part of reg   |

| csrrw  | rd,csr,rs1  | control & status register read & write   | X[rd] ← CSR[csr]; CSR[csr] ← rs1                           | writes entire reg  |

| csrw   | rs1,csr     | control & status register write          | CSR[csr] ← rs1                                             |                    |

| j      | imm         | unconditional branch                     | PC ← PC + sext(imm)                                        | imm ≠ value        |

| jal    | rd,imm      | Pr 11 20 W                               | X[rd] ← PC + 4; PC ← PC + sext(imm)                        | imm ≠ value        |

| jal    | imm         | unconditional branch with offset         |                                                            | rd=X1 if rd omito  |

| jalr   | rd,rs1,imm  |                                          |                                                            | imm ≠ value        |

| jalr   | rs1         | unconditional branch with offset & link  | X[rd] ← PC+4; PC ← (X[rs1] + sext(imm)) & ~1               | rd=X1 if rd omito  |

| jalr   | rs1,imm     |                                          | 10 m m m m m m m m m m m m m m m m m m m                   | ru-A i if ra omito |

| jr     | rs1         | unconditional branch to register address | PC ← X[rs1]                                                |                    |

| la     | rd, symbol  | load absolute address of symbol          | X[rd] ← &symbol                                            |                    |

| 1h     | rd imm(rel) | load buto                                | V[rd] - covt/ M[V[rc1] + covt/imm) 1 [7:0] \               |                    |

| jr    | rs1          | unconditional branch to register address | PC ← X[rs1]                                                           |

|-------|--------------|------------------------------------------|-----------------------------------------------------------------------|

| la    | rd,symbol    | load absolute address of symbol          | X[rd] ← &symbol                                                       |

| 1b    | rd,imm(rs1)  | load byte                                | X[rd] ← sext( M[X[rs1] + sext(imm) ] [7:0] )                          |

| lbu   | rd,imm(rs1)  | load byte unsigned                       | X[rd] ← zext( M[X[rs1] + sext(imm)] [7:0] )                           |

| 1h    | rd,imm(rs1)  | load halfword                            | X[rd] ← sext( M[X[rs1] + sext(imm) ] [15:0] )                         |

| 1hu   | rd,imm(rs1)  | load halfword unsigned                   | X[rd] ← zext( M[ X[rs1] + sext(imm) ] [15:0] )                        |

| li    | rd,imm       | load immediate                           | X[rd] ← imm                                                           |

| lw    | rd,imm(rs1)  | load word into register                  | X[rd] ← M[X[rs1] + sext(imm)] [31:0]                                  |

| lui   | rd,imm       | load upper immediate                     | X[rd] ← imm << 12                                                     |

| mret  |              | machine mode exception return            | PC ← CSR[mepc]; CSR[mstatus(mie) ← mstatus(mpie)                      |

| mv    | rd,rs1       | move                                     | X[rd] ← X[rs1]                                                        |

| neg   | rd,rs2       | negate                                   | X[rd] ← -X[rs2]                                                       |

| nop   |              | no operation                             | nada (PC ← PC + 4)                                                    |

| not   | rd,rs2       | ones complement                          | X[rd] ← ~X[rs2]                                                       |

| or    | rd,rs1,rs2   | bitwise inclusive OR                     | X[rd] ← X[rs1]   X[rs2]                                               |

| ori   | rd,rs1,imm   | bitwise inclusive OR immediate           | X[rd] ← X[rs1]   sext(imm)                                            |

| ret   |              | return from subroutine                   | PC ← X1                                                               |

| sb    | rs2,imm(rs1) | store byte in memory                     | M[ X[rs1] + sext(imm) ] ← X[rs2][7:0]                                 |

| seqz  | rd,rs1       | set if equal to zero                     | X[rd] ← ( X[rs1] == 0 ) ? 1 : 0                                       |

| sgtz  | rd,rs2       | set if greater than zero                 | $X[rd] \leftarrow (X[rs2] >_{s} 0) ? 1 : 0$                           |

| sh    | rs2,imm(rs1) | store halfword in memory                 | M[ X[rs1] + sext(imm) ] ← X[rs2][15:0]                                |

| sw    | rs2,imm(rs1) | store word                               | M[ X[rs1] + sext(imm) ] ← X[rs2]                                      |

| sll   | rd,rs1,rs2   | logical shift left                       | $X[rd] \leftarrow X[rs1] \ll X[rs2][4:0]$                             |

| slli  | rd,rs1,imm   | logical shift left immediate             | $X[rd] \leftarrow X[rs1] \le imm[4:0]$                                |

| slt   | rd,rs1,rs2   | set if less than                         | $X[rd] \leftarrow (X[rs1] \leq_s X[rs2]) ? 1 : 0$                     |

| slti  | rd,rs1,imm   | set if less than immediate               | X[rd] ← ( X[rs1] < <sub>s</sub> sext(imm) ) ? 1 : 0                   |

| sltiu | rd,rs1,imm   | set if less than immediate unsigned      | X[rd] ← ( X[rs1] <u )="" 0<="" 1="" :="" ?="" sext(imm)="" th=""></u> |

| sltu  | rd,rs1,rs2   | set if less than unsigned                | $X[rd] \leftarrow (X[rs1] \le X[rs2])?1:0$                            |

| sltz  | rd,rsl       | set if less than zero                    | $X[rd] \leftarrow (X[rs1] <_{s} 0) ? 1 : 0$                           |

| snez  | rd,rs2       | set if not equal to zero                 | X[rd] ← ( X[rs2] ≠ 0 ) ? 1 : 0                                        |

| sra   | rd,rs1,rs2   | arithmetic shift right                   | $X[rd] \leftarrow X[rs1] >>_s X[rs2] [4:0]$                           |

| srai  | rd,rs1,imm   | arithmetic shift right immediate         | $X[rd] \leftarrow X[rs1] >>_s imm[4:0]$                               |

| srl   | rd,rs1,rs2   | logical shift right                      | X[rd] ← X[rs1] >> X[rs2][4:0]                                         |

| srli  | rd,rs1,imm   | logical shift right immediate            | $X[rd] \leftarrow X[rs1] >> imm[4:0]$                                 |

| sub   | rd,rs1,rs2   | subtract                                 | $X[rd] \leftarrow X[rs1] - X[rs2]$                                    |

| xor   | rd,rs1,rs2   | exclusive OR                             | X[rd] ← X[rs1] ^ X[rs2]                                               |

| xori  | rd,rs1,imm   | exclusive OR immediate                   | X[rd] ← X[rs1] ^ sext(imm)                                            |

Table 13: RISC-V OTTER Instructions with RTL description.

1.6

# Thanks

Stick around CARP for more presentations in the future:

- Advanced CPU Architecture (CPE333 and Beyond)

- CPU vs. GPU Architecture

- Introduction to Research